MII\GMII\RGMII

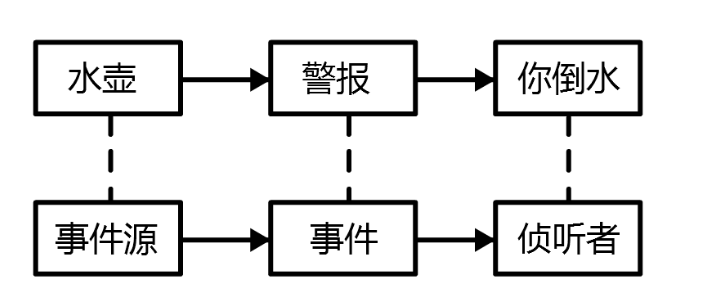

MDIO 是纯粹的控制接口,负责 MAC 与 PHY 之间的参数配置、状态读取;而 MII/GMII/RGMII 是数据通信接口,专门传输以太网帧的实际数据(收发双向),两者分工明确、协同工作,共同完成以太网的完整通信。

一、核心分工:控制 vs 数据

| 接口类型 | 核心作用 | 传输内容 | 总线特性 |

|---|---|---|---|

| MDIO | 控制与管理 | PHY 配置参数(速率、双工)、状态信息(链路是否连通) | 双线串行总线(MDC 时钟 + MDIO 数据),低速 |

| MII/GMII/RGMII | 数据收发 | 以太网帧(前导码、数据、CRC)、同步时钟、使能信号 | 多线并行总线(含数据、时钟、控制信号),高速 |

简单说:MDIO 是“指挥通道”(比如告诉 PHY“用1G全双工模式”),MII/GMII/RGMII 是“数据通道”(实际传输网页、文件等数据)。

二、数据接口的差异(MII/GMII/RGMII)

三者都是 MAC 与 PHY 之间的数据接口,核心区别是速率、信号线数量、时序设计,适配不同带宽需求:

MII(Media Independent Interface)

- 支持速率:10M/100M 以太网

- 信号线:共 16 根(发送侧 4 根数据 + TXEN/TXER + TXCLK;接收侧 4 根数据 + RXDV/RXER + RXCLK)

- 特点:低速、信号线多,适合早期百兆以太网设备

GMII(Gigabit MII)

- 支持速率:10M/100M/1G 以太网(向下兼容 MII)

- 信号线:共 24 根(发送侧 8 根数据 + TXEN/TXER + GTXCLK;接收侧 8 根数据 + RXDV/RXER + RXCLK)

- 特点:高速、带宽足,但信号线多,对 PCB 布线要求较高

RGMII(Reduced GMII)

- 支持速率:10M/100M/1G 以太网(兼容 GMII)

- 信号线:仅 12 根(发送侧 4 根数据 + TX_CTL;接收侧 4 根数据 + RX_CTL;时钟线 2 根)

- 特点:通过“边沿复用”技术减少信号线,兼顾高速和布线简便,是目前嵌入式设备(如 ARM 开发板)最常用的接口

三、实际工作流程(MAC + PHY 协同)

- 内核通过 MDIO 总线,配置 PHY 的工作模式(比如选择 RGMII 接口、1G 全双工、自动协商);

- 数据传输时,MAC 生成以太网帧,通过 RGMII/MII/GMII 接口的 TXD(发送数据)线输出,同时通过 TXEN(发送使能)信号标记数据有效;

- PHY 接收数据后,转换为物理电信号(如差分信号),通过网线传输;

- 接收数据时,PHY 将网线的电信号转换为数字信号,通过 RGMII/MII/GMII 接口的 RXD(接收数据)线传给 MAC,同时通过 RXDV(接收有效)信号告知 MAC 数据可用;

- 内核通过 MDIO 实时读取 PHY 的状态寄存器,获取链路速率、连接状态等信息(比如

ethtool命令的输出)。

MDIO、MII/GMII/RGMII这三类接口的核心参数、信号定义和关键差异,

我将以清晰的表格+分类说明的形式。

一、核心接口总览表(MDIO + MII/GMII/RGMII)

先通过总表快速掌握三类接口的核心属性,

其中MII/GMII/RGMII归为数据接口,MDIO为控制接口:

| 接口类型 | 核心用途 | 支持速率 | 信号线数量 | 总线类型 | 时钟频率/特性 | 典型应用场景 |

|---|---|---|---|---|---|---|

| MDIO | PHY配置/状态读取 | 低速控制 | 2根 | 串行 | MDC(2.5MHz~25MHz),双向MDIO | 所有以太网设备(MAC↔PHY) |

| MII | 以太网数据收发 | 10M/100M | 16根 | 并行 | TXCLK/RXCLK(25MHz/2.5MHz) | 早期百兆嵌入式设备 |

| GMII | 以太网数据收发 | 10M/100M/1000M | 24根 | 并行 | GTXCLK(125MHz)、RXCLK(125MHz) | 千兆以太网设备(PCB布线宽松) |

| RGMII | 以太网数据收发(精简版) | 10M/100M/1000M | 12根 | 并行 | TXCLK/RXCLK(125MHz/25MHz),边沿复用 | ARM嵌入式设备(开发板、工控机) |

二、分接口详细说明(信号定义+关键逻辑)

1. MDIO(控制接口:Media Independent Interface Management)

核心信号(仅2根,双向/单向区分明确):

| 信号名 | 方向 | 作用 |

|---|---|---|

| MDC | MAC→PHY | 管理时钟信号(MDIO总线的同步时钟,标准速率最高25MHz,常用2.5MHz) |

| MDIO | 双向(MAC↔PHY) | 管理数据信号(MAC发送配置命令/读取PHY状态,PHY返回状态数据,半双工) |

关键逻辑:

- MDIO采用地址+寄存器的访问机制:MAC通过MDIO发送PHY地址(5位,最多32个PHY)、寄存器地址(5位)和读写命令,PHY响应并返回数据(16位寄存器值)。

- 内核中对应驱动路径:

drivers/net/phy/mdio_bus.c(MDIO总线核心)、drivers/net/phy/phy_device.c(PHY设备管理)。

2. MII(数据接口:Media Independent Interface)

核心信号(分发送、接收、时钟三类,共16根):

| 信号组 | 信号名 | 方向 | 作用 |

|---|---|---|---|

| 发送侧 | TXD[3:0] | MAC→PHY | 4位并行发送数据(10M/100M速率下的核心数据总线) |

| TXEN | MAC→PHY | 发送使能(高电平表示TXD数据有效) | |

| TXER | MAC→PHY | 发送错误(高电平表示当前TXD数据存在编码错误) | |

| TXCLK | PHY→MAC | 发送时钟(100M时25MHz,10M时2.5MHz,由PHY提供) | |

| 接收侧 | RXD[3:0] | PHY→MAC | 4位并行接收数据 |

| RXDV | PHY→MAC | 接收有效(高电平表示RXD数据有效,替代TXEN的接收侧版本) | |

| RXER | PHY→MAC | 接收错误(高电平表示当前RXD数据存在错误) | |

| RXCLK | PHY→MAC | 接收时钟(频率与TXCLK一致,由PHY提供) | |

| 其他 | CRSDV | PHY→MAC | 载波侦听/接收有效(部分场景复用RXDV) |

| COL | PHY→MAC | 冲突检测(半双工模式下的冲突指示) |

关键逻辑:

- 4位数据总线决定了100M速率下,需要25MHz时钟(4bit×25MHz=100Mbps)才能满足带宽。

- 仅支持百兆及以下速率,是早期以太网的标准数据接口。

3. GMII(数据接口:Gigabit MII)

核心信号(在MII基础上扩展为8位数据,共24根):

| 信号组 | 信号名 | 方向 | 作用 |

|---|---|---|---|

| 发送侧 | TXD[7:0] | MAC→PHY | 8位并行发送数据(支持千兆速率的核心扩展) |

| TXEN | MAC→PHY | 发送使能(与MII逻辑一致) | |

| TXER | MAC→PHY | 发送错误(与MII逻辑一致) | |

| GTXCLK | MAC→PHY | 千兆发送时钟(125MHz,由MAC提供,区别于MII的PHY提供时钟) | |

| 接收侧 | RXD[7:0] | PHY→MAC | 8位并行接收数据 |

| RXDV | PHY→MAC | 接收有效(与MII逻辑一致) | |

| RXER | PHY→MAC | 接收错误(与MII逻辑一致) | |

| RXCLK | PHY→MAC | 接收时钟(125MHz,由PHY提供) | |

| 其他 | 保留MII的CRSDV/COL | — | 向下兼容MII的冲突检测/载波侦听 |

关键逻辑:

- 8位数据总线+125MHz时钟(8bit×125MHz=1000Mbps),实现千兆速率。

- 信号线数量多(24根),对PCB布线的时序和抗干扰要求高,适合工业级设备(而非小型嵌入式板卡)。

4. RGMII(数据接口:Reduced GMII)

核心信号(精简版GMII,通过边沿复用减少信号线,共12根):

| 信号组 | 信号名 | 方向 | 作用 |

|---|---|---|---|

| 发送侧 | TXD[3:0] | MAC→PHY | 4位并行发送数据(通过时钟上升/下降沿复用,等效8位数据) |

| TX_CTL | MAC→PHY | 发送控制(复用TXEN和TXER,上升沿传TXEN,下降沿传TXER) | |

| TXCLK | PHY→MAC | 发送时钟(125MHz=千兆,25MHz=百兆,2.5MHz=十兆) | |

| 接收侧 | RXD[3:0] | PHY→MAC | 4位并行接收数据(同理边沿复用) |

| RX_CTL | PHY→MAC | 接收控制(复用RXDV和RXER,上升沿传RXDV,下降沿传RXER) | |

| RXCLK | PHY→MAC | 接收时钟(频率与TXCLK一致) |

关键逻辑(ARM嵌入式场景的核心优势):

- 边沿复用技术:在时钟的上升沿和下降沿分别传输1位控制信号/4位数据,实现用4位数据总线达到GMII 8位的带宽,信号线数量减少一半。

- 是目前ARM开发板(如树莓派、NXP i.MX、瑞芯微RK系列)的标配以太网数据接口,兼顾高速和布线简便。

三、ARM架构下的接口关联逻辑(设备树视角)

在ARM平台的设备树(DTB)中,MDIO和RGMII/MII/GMII是关联配置的,典型逻辑:

- MAC控制器节点中,同时声明MDIO总线节点和RGMII数据接口节点;

- MDIO节点通过

phy-handle指向PHY设备节点,PHY节点中声明compatible(PHY型号)和reg(PHY地址,MDIO访问用); - 数据接口节点声明引脚复用(如TXD0~TXD3、TX_CTL、TXCLK)和速率配置(如千兆全双工)。

总结

- MDIO是控制接口,仅2根线,负责MAC对PHY的配置和状态读取,是所有以太网设备的必备接口。

- MII是百兆数据接口,16根线,4位数据总线,仅支持10/100M速率,属于早期标准。

- GMII是千兆数据接口,24根线,8位数据总线,支持千兆速率但布线复杂;RGMII是其精简版,通过边沿复用减少信号线,是ARM嵌入式设备的主流选择。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 naro!